# The Skewed Distribution of Working Sets: Leveraging Randomness for Cache Design

Thesis submitted for the degree of

"Doctor of Philosophy"

by

Yoav Etsion

Submitted to the Senate of the Hebrew University

October / 2008

This work was carried out under the supervision of

### Prof. Dror G. Feitelson

# Acknowledgements

To my beloved Adina, for the loving support and never ending acceptance, and for never laughing out loud when I said I'm simply thinking about my research with my eyes closed.

To my advisor Dror Feitelson (who I still suspect was not in his right mind to take me as a student), for being a true role model and mentor, and for giving real meaning to the title of an academic father.

To my parents, for believing despite what all the teachers said.

And finally to my feisty son Yotam: although you only recently joined the team, your smile makes all the difference, redhead.

### Abstract

The increasing gap between processor and memory speeds, as well as the introduction of multicore CPUs, have exacerbated the dependency of CPU performance on the memory subsystem. This trend motivates the search for more efficient caching mechanisms, enabling both faster service of frequently used blocks and decreased power consumption.

This thesis explores the temporal locality phenomenon in an effort to devise such efficient caching mechanisms. Specifically, it is shown that while Denning's working sets model puts all memory blocks in a working set on an equal footing, a dramatic difference in fact exists between the usage patterns of frequently used data and those of lightly used data. This thesis therefore extends Denning's definition with the *core* working sets model, employing predicates to identify the most important subset of blocks in a working set.

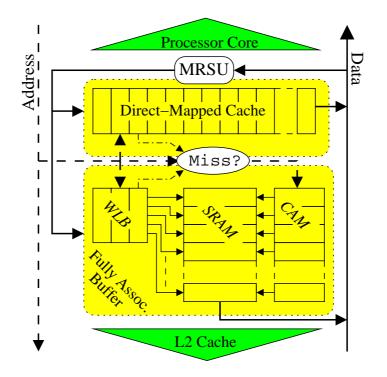

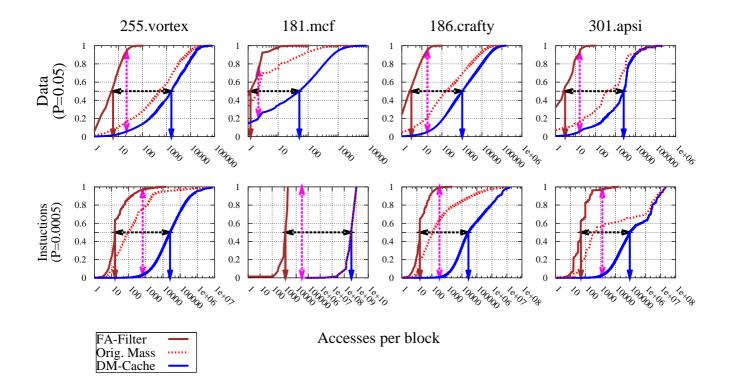

This model forms the base for a probabilistic predictor that can distinguish transient cache insertions from non-transient ones. It is shown that this predictor can identify a small set of data cache resident blocks that service most of the memory references. This predictor is then used in the design of an L1 dual-cache that inserts only frequently used blocks into a low-latency, low-power direct-mapped main cache, while serving the rest of the blocks from a small fully-associative filter. The design further employs a novel, low-latency, low-power fully-associative element, that uses a small direct-mapped lookup table to cache recently accessed blocks in the filter — thereby eliminating most of the costly fully-associative lookups.

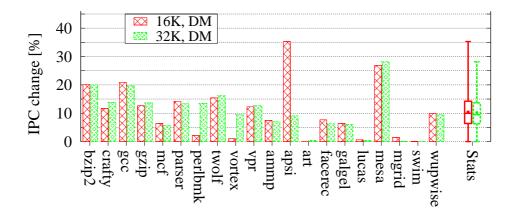

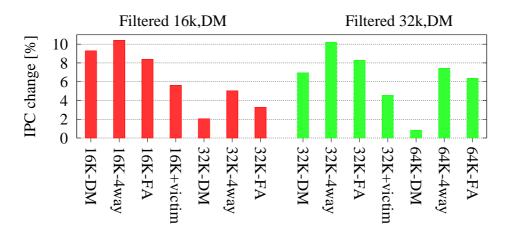

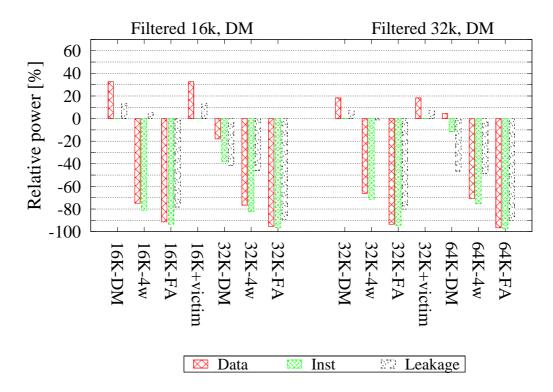

This L1 dual-cache design demonstrates that a 16K direct-mapped L1 cache, augmented with a fully-associative 2K filter, can outperform a 32K 4-way cache, while consuming 70%-80% less dynamic power and 40% less static power.

# Contents

| 1 | Introduction |                                                                                 |    |  |  |

|---|--------------|---------------------------------------------------------------------------------|----|--|--|

|   | 1.1          | Background                                                                      | 1  |  |  |

|   | 1.2          | The Mass-Count Disparity Phenomenon and                                         |    |  |  |

|   |              | Core-Working-Sets                                                               | 4  |  |  |

|   | 1.3          | Leveraging Randomness for L1 Cache Design                                       | 5  |  |  |

|   | 1.4          | List of Publications Composing this Work                                        | 6  |  |  |

|   | 1.5          | Main Contributions of this Work                                                 | 7  |  |  |

| 2 | Met          | hodology                                                                        | 9  |  |  |

| 3 | The          | Skewed Distribution of Memory Accesses and the Mass-Count Disparity Phe-        |    |  |  |

|   | nomenon      |                                                                                 |    |  |  |

|   | 3.1          | Cache Residency Length: A New Metric for Rating Temporal Locality of            |    |  |  |

|   |              | Memory Blocks                                                                   | 13 |  |  |

|   | 3.2          | Mass-Count Disparity in L1 Workloads                                            | 16 |  |  |

| 4 | Cor          | e Working Sets: Capturing the Dual Nature of Memory Workloads                   | 29 |  |  |

|   | 4.1          | Definition of Core Working Sets                                                 | 32 |  |  |

|   | 4.2          | Core Working Sets and Dual Cache Structures                                     | 34 |  |  |

| 5 | Cac          | he Filtering Through Probabilistic Prediction of Temporal Locality              | 39 |  |  |

|   | 5.1          | On the Non-Feasibility of an Optimal Insertion Policy for Dual-Cache Structures | 40 |  |  |

|   | 5.2          | Identifying An Effective Subset of Blocks                                       | 42 |  |  |

| Bil | Bibliography |                                                             |    |  |  |  |  |  |

|-----|--------------|-------------------------------------------------------------|----|--|--|--|--|--|

| 8   | Con          | clusions                                                    | 91 |  |  |  |  |  |

|     | 7.5          | Efficient Use of Direct-Mapped and Fully-associative Caches | 88 |  |  |  |  |  |

|     | 7.4          | Partitioning the Reference Stream                           | 84 |  |  |  |  |  |

|     | 7.3          | Probabilistic Filtering                                     | 83 |  |  |  |  |  |

|     | 7.2          | Strategies for Operating Systems' Buffer Caches             | 82 |  |  |  |  |  |

|     | 7.1          | Mass Count Disparity                                        | 81 |  |  |  |  |  |

| 7   | Rela         | ted Work                                                    | 79 |  |  |  |  |  |

|     | 6.4          | Impact on Power and Performance                             | 74 |  |  |  |  |  |

|     | 6.3          | The Wordline Look-aside Buffer                              | 71 |  |  |  |  |  |

|     |              | 6.2.2 Impact on Reference Distribution                      | 62 |  |  |  |  |  |

|     |              | 6.2.1 Impact on Miss-Rate                                   | 61 |  |  |  |  |  |

|     | 6.2          | The Effects of Random Sampling                              | 60 |  |  |  |  |  |

|     | 6.1          | Proposed Design                                             | 58 |  |  |  |  |  |

| 6   | A Ra         | andom Sampling L1 Cache Design                              | 57 |  |  |  |  |  |

|     | 5.4          | Evaluating the Probabilistic Predictor                      | 47 |  |  |  |  |  |

|     | 5.3          | Probabilistic Residency Length Predictor                    | 45 |  |  |  |  |  |

# Chapter 1

### Introduction

### 1.1 Background

The notion of a memory hierarchy is one of the oldest and most ubiquitous in computer design, dating back to the work of von Neumann and his associates in the 1940's. The idea is that a small and fast memory will cache the most useful items at any given time, with a larger but slower memory serving as a backing store [27, 32, 70].

As the essence of caching is to identify and store those data items that will be most useful in the immediate future [6], caches need to predict which items will be used in the immediate future. These predictions ubiquitously rely on the principle of locality, which states that at any given time only a small fraction of the whole address space is used, and that this used part changes relatively slowly [19]. Denning formalized this using the notion of a *working set*, defined to be those items that were accessed within a certain number of instructions. The goal of caching is thus effectively to keep the working set in the cache.

The effectiveness of caching thus relies on the existence of working sets, as these represent a subset of all memory blocks that are in current use. But working sets are not homogeneous, as some memory blocks are more popular than others [35]. This heterogeneous nature of working sets raises the question whether caches should employ a heterogeneous design rather than the common random-access paradigm, as processors can benefit if the more popular blocks in the working set (and in general) are treated beneficially by the cache by serving them faster. One way to give preferential treatment to the more important data elements is to use a *dual* cache structure. Such structures partition the cache into two parts, and use them for data elements that exhibit different access patterns  $[65]^1$ . In many cases, data elements can also move from one part to the other. For example, data may first be stored in a short-term buffer, and only data that is identified as important will be promoted into the long-term cache. The identification of a certain item as important can be done based on the references it received while in the shortterm buffer: if it is referenced again and again, it is identified as part of the core and promoted. The concept of dual-cache designs has been extensively explored in the past, specifically in the context of filtering memory references [12, 33, 36, 37, 39, 40, 46, 62, 64, 65, 63, 79]. But while dual-cache designs offer flexibility, the filtering of memory blocks has proven difficult as it ordinarily requires maintaining information about memory blocks' previous usage patterns in order to predict future use. The mechanisms required to implement the filtering, and specifically those involved with maintaining past reuse information, have thus been deemed largely impractical, due to the number of transistors they require (with the corresponding die area) and the power they consume.

The increasing gap between processor and memory speeds witnessed in recent years has exacerbated the CPU's dependency on the memory system performance — and especially that of L1 caches with which the CPU interfaces directly. One result of this ongoing trend is the increase in the capacity of L1 and L2 caches, in an effort to bridge the memory-processor gap and improve overall system performance. This improvement, however, also increases the power consumed by the caches — estimated at more than 10% of the overall power consumed by a general purpose CPU [31], and up to 40% for embedded systems [9].

Recent years have seen a shift in processor design, as the increase in CPU clock speeds witnessed for some 30 years have largely ground to a halt, due to several inherent physical limitations [52, 61, 81]: example limitations include wire delays preventing the propagation of fast clock signals uniformly to all parts of the chip; shrinking Silicon features made possible by

<sup>&</sup>lt;sup>1</sup>We differentiate this from a *split* cache structure, where one part is used for data and the other for instructions, but some authors use the terms interchangeably.

new process manufacturing improvements hindered transistor gate isolation and increase power leakage; and increased clock frequency drove designers to employ longer, more complicated pipelines, thwarting most of the theoretical performance increase made possible by the faster clock frequency.

These shifts in technology have increased processors' power density and have elevated processor power consumption into a major concern. Today, the power-performance tradeoff is ever more important. This trend motivates researchers to design more efficient caches, that can deliver performance while maintaining a power budget. Furthermore, despite predictions, transistor density continued to grow as predicted by Moore's Law [47, 48, 66]. The continued increase in transistor density and the limitations in increasing processor frequency caused the microprocessor industry to focus on on-chip parallelism, available by placing multiple processing cores on a single chip — also known as chip multiprocessors (CMP) [22, 25, 41]. This in turn, has made the power consumption of caches an even bigger concern, as multi-core CPUs typically replicates the L1 caches for each core to avoid the design complexities of multiple processors sharing an L1 cache [49].

The increasing concern regarding cache power consumption, together with the increased memory bandwidth requirements of multiple cores sharing a memory bus [10], have motivated a quest for improved utilization of cache resources through the design of more efficient caching structures. This quest solicits a revisit to existing ideas such as dual cache structures, specifically ones incorporating direct-mapped cache structures. Direct-mapped caches are very appealing in this context, as they are faster and consume less energy than set-associative caches typically used in L1 caches [28, 38]. However, they are more susceptible to conflict misses than set-associative caches, thus suffering higher miss-rates and achieving lower performance. This deficiency led to abandoning direct-mapped L1 caches in favor of set-associative ones in practically all but embedded processors.

The quest for more efficient caches relies on extensive analysis of memory workloads, and the development of new analysis tools enabling a deeper understanding of cache behavior. The rest of this chapter therefore introduces the workload analysis concepts explored in this work (Section 1.2), and gives a peek into the insights gained by the workload analysis, and the ensuing cache design incorporating these insights (Section 1.3).

# 1.2 The Mass-Count Disparity Phenomenon and Core-Working-Sets

It is well known that memory block popularity is skewed, and some blocks are more popular than others. However, little is known about the scale of this phenomenon and how extreme is the variation in the popularity of the various memory blocks. For caching purposes, the identification of the most popular blocks is of utmost importance as it allows caching mechanisms to make sure these blocks — servicing very many residencies — are cached. Moreover, the exact subset of popular blocks changes during program execution as it passes through different computing phases. Denning attempted to capture this changing subset of blocks in his definition of *working sets* [17].

The need to identify memory usage patterns, therefore, motivated an extensive analysis of memory workloads. This analysis, described in Chapter 3, reveals that the skew in block popularity is even more extreme than thought before, and experiences a statistical phenomenon called the *Mass-Count Disparity*. The phenomenon describes the relationship between the number of memory references serviced by each single memory block, and how *all* memory references are distributed between the different blocks. Effectively, it reveals that the vast majority of memory references are commonly serviced by a tiny fraction of all memory blocks. In addition, the analysis reveals that even the relatively unpopular blocks experience bursty access patterns.

These results suggests that locality, usually regarded as a combination of two distinct properties — locality in time and locality in space — is also a manifestation of the skewed distribution of the *popularity* of different memory blocks, where some blocks are accessed much more frequently than others. In fact, it may be possible to partition the working set into two sub-sets: those memory blocks that are very popular and are accessed at a very high rate, and those that are only accessed intermittently. This distinction is antithetical to Denning's definition which puts all items in a working set on an equal footing, and lies at the heart of our definition of the *core* of the working set.

The notion of a core leads to the realization that not all elements of the working set are equally important. As the elements in the working set are not accessed in a homogeneous manner, treating all the elements of the working set equally may lead to sub-optimal performance. Rather, it may be beneficial to try to identify the more important core elements, and give them preferential treatment.

The notion of a popular core leads to the formal definition of a *Core Working Set*, described in Chapter 4 as an extension to Denning's working set. By using logical predicates to identify this highly popular subset of the entire working set, core working sets devise a formal framework serving designers of caching mechanisms to explicitly express their notion of the working set's core, that is to be treated beneficially by their design. In addition, this framework enables designers to compare and contrast the mechanism's performance against the formal definition of their intended core.

### 1.3 Leveraging Randomness for L1 Cache Design

The existence of a small core that governs the majority of memory references is described by the mass-count disparity phenomenon. But the phenomenon also implies the opposite — that the majority of memory blocks only service a small fraction of all memory references. These two consequences of the mass-count disparity phenomenon lend themselves to the application of simple, stateless, random sampling in order to partition the reference stream. As most memory blocks are accessed a small number of times, picking a block at random will likely select a block that is rarely accessed. In fact, this is the reason why a random eviction policy yields fairly good results [70, 67]. But on the other hand, since most memory references are serviced by a small fraction of the working set, a randomly selected *memory reference* likely pertains to a very popular block.

This observation is the corner stone for the probabilistic popularity predictor presented in Chapter 5. In turn, the probabilistic predictor is used in the design a random sampling L1 filtered cache, described in Chapter 6, that uses simple coin tosses to preferentially insert only frequently used blocks into the cache — composed of a fast, low-power direct-mapped structure — that services the majority of memory reference. The rest of the references are serviced from the cache's filter — a small fully-associative auxiliary structure — thus reducing the number of conflict misses in the direct-mapped cache. This mechanism is shown to use a simple filtering strategy to overcome the direct-mapped susceptibility to conflict misses, thereby enabling to harness the speed and low power traits of direct-mapped caches to reduce the overall L1 power consumption, while still improving overall performance.

This is the first successful attempt that employs a simple statistical phenomenon to filter both L1 reference streams efficiently enough to use a direct-mapped structure for L1 caches, thus both reducing power consumption and improving performance.

### **1.4** List of Publications Composing this Work

The research presented in this thesis is described in the following publications:

• Yoav Etsion and Dror G. Feitelson, Core Working Sets: Concept, Identification, and Use.

Submitted for Publication.

Also published as *Technical Report 2008-64*, School of Computer Science and Engineering, The Hebrew University of Jerusalem, Jul. 2008.

Yoav Etsion and Dror G. Feitelson, L1 Cache Filtering Through Random Selection of Memory References.

In Parallel Architectures and Compilation Techniques (PACT), pages 235-244, Sep. 2007.

• Yoav Etsion and Dror G. Feitelson, **Probabilistic Prediction of Temporal Locality**. In *IEEE Computer Architecture Letters (CAL)*, 6(1), pages 17-20, May 2007.  Yoav Etsion and Dror G. Feitelson, Cache Insertion Policies to Reduce Bus Traffic and Cache Conflicts.

*Technical Report 2006-4*, School of Computer Science and Engineering, The Hebrew University of Jerusalem, Feb. 2006

### **1.5** Main Contributions of this Work

For brevity, following is a list containing the main contributions of this research.

#### • L1 Cache Workload Analysis and the Mass-Count Disparity Phenomenon

The foundation of this work is a detailed analysis of L1 cache workloads, and the resulting characterization of the mass-count disparity phenomenon in L1 caches (Chapter 3).

#### • Core Working Sets

The definition of the predicate based *core working set* framework. This framework extends Denning's definition of working sets to accommodate their heterogeneous nature. The framework enables cache designers to explicitly express their perception of the important subset of the memory blocks (Chapter 4).

#### Probabilistic Block Popularity Predictor

A simple application of the mass-count disparity phenomenon offers the use of random sampling of memory reference to probabilistically identify popular memory blocks in a completely stateless fashion, without any need for maintaining past use information (Chapter 5).

#### • Random Sampling L1 Filtered Cache

The proposed L1 cache design is based on the dual-cache paradigm and uses random sampling to filter out transient blocks and identify the small fraction of popular memory blocks. This partitioning of the working set enables the use of a fast, low-power direct-mapped structure to serve the majority of memory references, thereby improving overall performance and reducing the power consumed by L1 caches (Chapter 6).

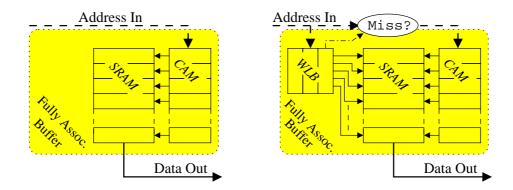

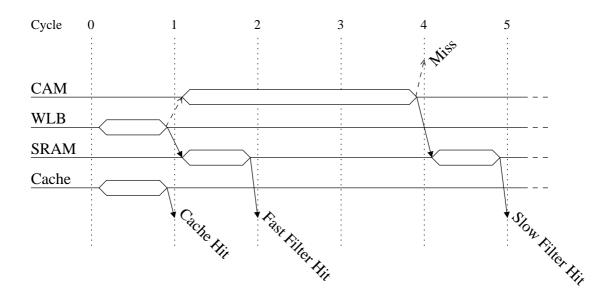

#### • Wordline-Lookaside-Buffer (WLB)

A problem with the fully-associative filter is its access time and power consumption. We alleviate this problem using a small lookup table that harnesses temporal locality to cache expensive fully-associative lookups in a small inexpensive direct-mapped table. The WLB therefore reduces both access times and power consumption of fully-associative caches, without affecting the fully-associative semantics (Chapter 6).

The methodology used throughout the research is discussed in Chapter 2. Following the description of the research itself (Chapters 3 through 6), the body of work in the field is reviewed in Chapter 7.

# **Chapter 2**

### Methodology

Extracting and analyzing memory and cache workloads, as well as the evaluation of alternative hardware designs, require software simulations of both existing and proposed architectures. The simulator that was used to carry out all simulations in this work is the *SimpleScalar* simulation toolset [4], simulating the *Alpha AXP* architecture [69].

Accounting for all aspects of the simulated architecture with a full simulation of all implementation details is an arduous task, resulting in excruciatingly slow simulations. The SimpleScalar toolset is therefore broken into several individual, yet co-dependent tools that simulate the underlying hardware with varying degrees of detail, thereby trading off simulation accuracy for speed. Of the different tools, the ones used were:

- **sim-fast** is a functional simulator that only simulates the ISA. By ignoring all implementation details of the underlying architecture it essentially simulates an optimal architecture that incurs no inherent latencies. It is therefore the fastest tool in the toolchain, but cannot be used to measure performance. In our case, *sim-fast* was augmented to collect raw workload statistics that are largely independent on architectural implementation details.

- **sim-cache** is a cache simulator. It can be seen as an extension of *sim-fast* that implements a full cache hierarchy to collect cache statistics such as hit-rate. Although *sim-cache* is oblivious of any statistical artifacts caused by full out-of-order execution, it was found

accurate enough for collecting cache statistics. To evaluate cache performance of alternative cache designs, *sim-cache*'s cache module was completely rewritten to support the proposed cache design.

• **sim-outorder** simulates a detailed out-of-order processor. It is the most detailed simulation tool in the SimpleScalar toolset, and is therefore the slowest. *sim-outorder* was used to evaluate the effect of proposed caching mechanism on the overall architecture performance, and specifically on metrics such as IPC (instructions-per-cycle). The modifications to *sim-outorder* include replacing its cache module with one supporting the proposed cache design, and since this design is based on the dual-cache paradigm, its instruction scheduling algorithm was slightly modified to accommodate for variable L1 hit latencies. The original algorithm is based on the common practice in superscalar designs that schedule instructions based on the prediction that the L1 hits [67]. This modification was needed since L1 hits can now hit either in the cache proper or the auxiliary filter, where each has different hit latencies. The algorithm was simply extended to predict that the L1 hits, and the hit is services by the cache proper, with its associated latency — thus extending the common practice in an obvious manner.

The benchmarks used consisted on the *SPEC2000* benchmarks suite [72]. An overall of 20 benchmarks were used in order to accommodate as many different workloads [15]. This constitutes of all but six SPEC2000 benchmarks: *eon, gap, fma3d, sixtrack,* and *applu* failed to either compile or execute, and *equake* experienced too few L1 misses (under 0.02%) on both data and instruction streams to produce meaningful results. All benchmarks were executed with the *ref* input set and were fast-forwarded 15 billion  $(15 \times 10^9)$  instructions to skip any initialization code (except for *vpr* whose full run is shorter), and were then executed for another 2 billion  $(2 \times 10^9)$  instructions.

Power estimates were compiled using *CACTI*, an integrated cache and memory model that evaluates access time, cycle time, area, leakage, and dynamic power. The version used was 4.1, configured for a 70nm manufacturing process [75] (the finest feature size CACTI supports).

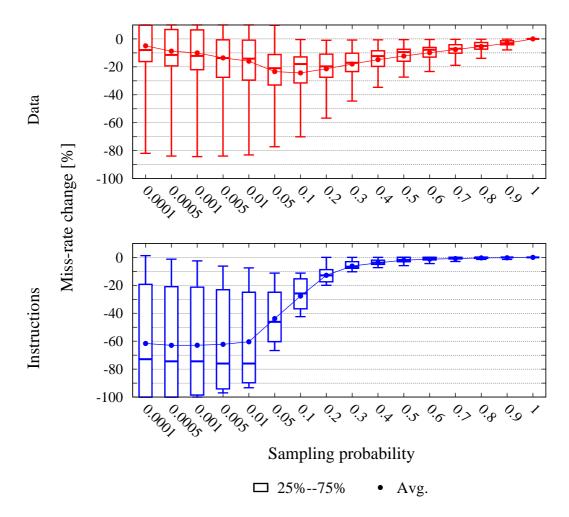

Throughout the thesis, whenever results are shown for all benchmarks, they are summarized using box-plots. The boxes show the 25th, 50th (median) and 75th percentiles over all the benchmarks' results. In addition, these plots include whiskers to show the minimum and maximum values, and a circle marking the average value.

### Chapter 3

# The Skewed Distribution of Memory Accesses and the Mass-Count Disparity Phenomenon

*Mass-Count Disparity* is a statistical phenomenon describing a situation where most items in a population are small, but a few are very large (also known as "mice & elephants" in networking [8]). The name *mass-count disparity* comes from the distinctly disjoint nature of two conjoining distributions — that of the sizes of individual elements (count distribution), and how the overall mass is distributed across elements of different sizes (mass distribution). Perhaps the most well-known example of mass-count disparity is an economic one, namely the distribution of wealth in the world [43]: with most people in the world being relatively poor, and only a tiny fraction of the entire population is very rich, the majority of world's wealth (the aggregate sum of all the world population's financial resources) is dominated by a very small fraction of the population. Other known examples are WWW connectivity [83] and file sizes vs. disk space [30].

Formally, given a finite sample space the mass-count disparity phenomenon refers to the interplay of two conjoined yet opposed distributions defined over that space. The first distribution — called the *count* distribution — is a distribution over the individual samples. Thus,  $F_c(x)$  represents the probability that a sample has a mass smaller than x. Following the economic example, this represents the fraction of the world's population whose individual wealth

is smaller than x currency units. The second distribution — called the *mass* distribution — is a distribution over the aggregate mass of all individual samples.  $F_m(x)$  represents the probability that a mass unit is part of a sample whose total mass is smaller than x. In our economic example, this represents the probability that a currency unit belongs to a person whose wealth is smaller than x currency units.

The disparity between the two distributions exists when the count probability  $F_c(x)$  is likely to be high, but the corresponding mass probability  $F_m(x)$  is likely to be low. In our economic example, this is demonstrated in the fact that most of the world population is poor, therefore the count probability indicating the fraction of individuals whose total wealth is smaller than say  $100 - F_c(100)$  is high. On the other hand, since most of the world's wealth is dominated by rich people, the probability that some arbitrary Dollar of all the money in the world belongs to an individual whose wealth is smaller than  $100 - F_m(100)$  is very low.

The mass-count disparity phenomenon has interesting implications regarding the identification of the small fraction of samples dominating the mass. The rest of this chapter describes a novel caching efficiency metric — *Cache Residency Length* — and uses this metric to uncover a clear manifestation of the mass-count disparity phenomenon in both data and instruction memory reference streams.

# 3.1 Cache Residency Length: A New Metric for Rating Temporal Locality of Memory Blocks

Evaluating the relative importance of a memory block for caching purposes requires assessing both its momentary and global popularity. The naive solution would be counting the number of references made to each block, and rating the blocks by their sheer popularity. A possible refinement to this general popularity scaling can be achieved by using a specific window of memory references of a predetermined size, and rating blocks' importance based on their popularity within a window of references.

Either Block-Popularity metrics share a major caveat, as they consider all the references to

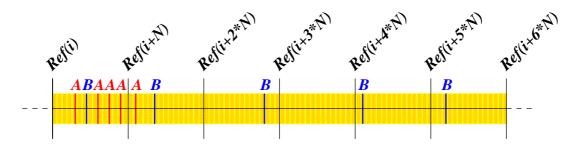

Figure 3.1: Comparison of the Cache Residency metric vs. the more common Block Popularity metric. The figure shows the dispersion of accesses to blocks A and B throughout a window of  $6 \times N$  memory references. Using the naive block popularity metric puts both blocks on an equal rating. On the other hand, the Cache Residency Length metric will separate the two blocks: Block B is sparsely used and therefore has a small impact on cache performance, which will likely manifest in a few short residencies. Block A is however densely used at the beginning of the window, and is therefore likely to have a long cache residency, corresponding with its bigger impact on cache performance.

each address, made throughout an arbitrary sized reference window (or simply throughout the duration of the run). But the relative popularity of different addresses may change in different phases of the computation, so the instantaneous popularity may be more important for caching studies. Using arbitrary sized reference windows further amplifies this problem, since the size of the window may determine the outcome of the measurement, as it may or may not be aligned with program phases and instantaneous program memory load.

We therefore propose *not* to use a predetermined window of references, but rather to count the number of references made between a single insertion of a block into the cache, and its corresponding eviction. This is denoted as a *cache residency length*. Thus, if a certain block is referenced 100 times when it is brought into the cache for the first time, is then evicted, and finally is referenced again for 200 times when brought into the cache for the second time, we will consider this as two distinct cache residencies spanning 100 and 200 references, respectively, rather than a single block with 300 references.

Figure 3.1 demonstrates the difference between the two metrics: it shows the use of two blocks that are accessed over a window of  $6 \times N$  references, where the references to each block are dispersed differently. While block *A* is densely used only at the beginning of the reference window, block *B* is referenced the same number of times, but these references are dispersed roughly evenly throughout the  $6 \times N$  references in the window.

Block *A* reference density indicates it affects cache performance more substantially than block *B*. This is supported by Belady's optimal cache replacement algorithm which always replaces the block whose next use is furthest away in the future [6], indicating block *A*'s reuse frequency will increase its importance to cache performance during the period it is used. The block popularity metric on the other hand evaluates the entire reference window, and will therefore put both blocks on an equal footing with 5 references each. In addition, even if we reduce the reference window size to *N*, the first window  $[i \dots i + N]$  will give a higher rating to block *A* — as it is used 4 times more than block *B* in that reference window — but, it will rate both blocks equally on the second  $[i + N \dots i + 2 \times N]$ , although the access to block *A* during that period is likely to hit in the cache as it is a continuation of the sequence of references to it which started during the previous reference window. Such an inconsistency between the block popularity metric's evaluation of a block's importance and its actual impact on cache performance is caused by the arbitrariness of the reference window size and alignment, which does not reflect the program's memory phases.

This example demonstrates that arbitrary sized reference windows, as used by the block popularity metric, may cause incorrect evaluation of the memory workload. On the other hand, the *Cache Residency Length* will likely include all reference to block *A* as a single cache residency, while block *B* will show as multiple shorter residencies. In this manner, this metric incorporates momentary cache load and reference density, and is thus better suited to rate the temporal locality experienced by different blocks.

One deficiency of the cache residency length metric is that it depends on a specific cache configuration. For example, increasing the cache size to infinity would converge the residency length metric with overall block popularity. On the other hand, using a degenerate cache consisting of a single block will limit all residencies to a single access (assuming a collapsed reference stream that counts consecutively repeating accesses to the same block as a single access). However, experimenting with different cache parameteres — such as set-associativity and cache size — revealed that applications' intrinsic memory behavior are sufficiently dominant and remain largely unaffected by small variations in cache configuration. Despite the

obvious changes to the specific details of residency length distributions, the overall probabilistic trends showed resilience to varying parameters.

Still, in order to maintain consistency it is important to maintain the same cache configurations when comparing results. This thesis uses a 16K direct-mapped configuration as standard, and differing configurations are clearly marked.

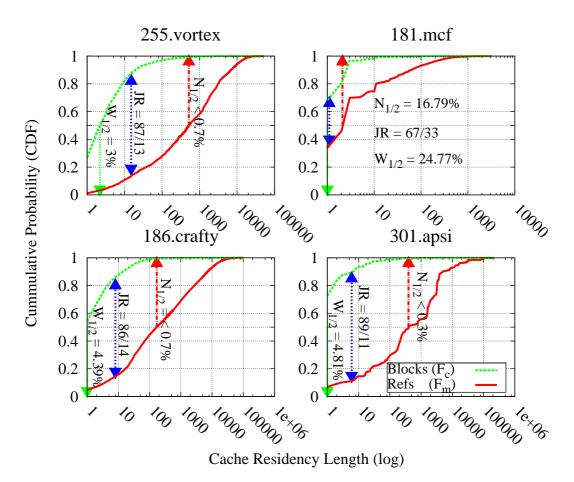

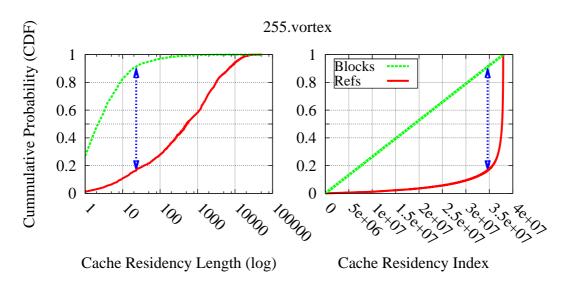

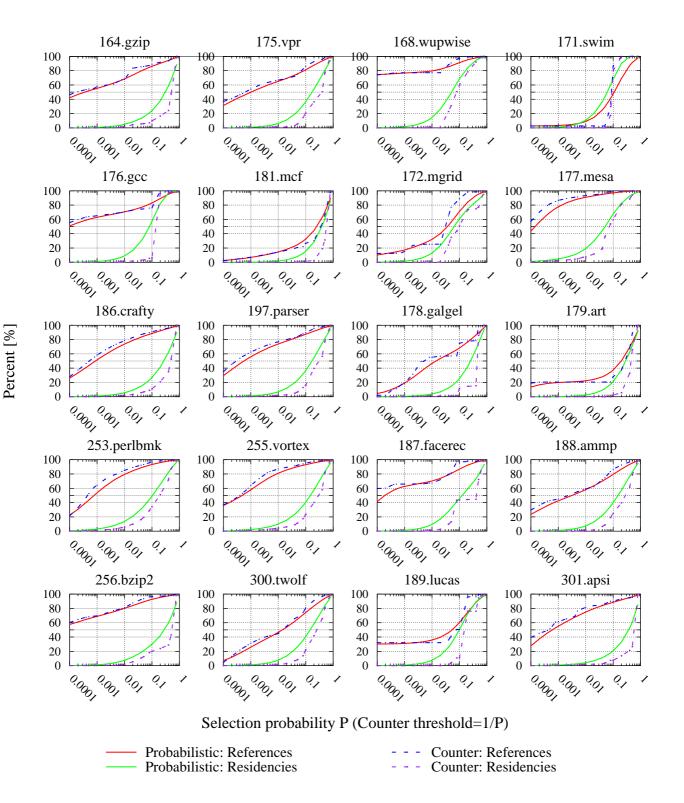

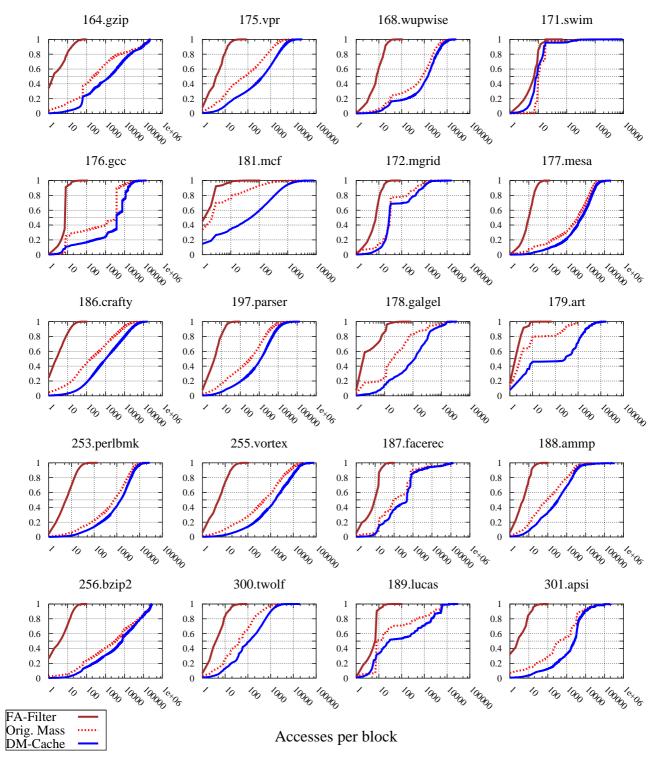

Figure 3.2: Mass-count disparity plots for **data** memory accesses in select SPEC 2000 benchmarks. The arrows demonstrate the  $W_{1/2}$ , joint-ratio, and  $N_{1/2}$  metrics of mass-count disparity.

### **3.2 Mass-Count Disparity in L1 Workloads**

The *Residency Length* metric enables us to demonstrate the existence of the mass-count disparity phenomenon of memory workloads. In our case, the count distribution  $F_c(x)$  represents the probability that a block's residency length is composed of x references or less. The *mass* distribution on the other hand, is a distribution on references; it specifies the popularity of the block to which the reference pertains. Thus  $F_m(x)$  represents the probability that a reference is directed at a residency composed of x references or less. The disparity is visualized using mass-count disparity plots [20]. These plots superimpose the two distributions.

The mass-count disparity plots show that the graphs of the count and mass distributions are quite distinct. An example is shown in Figure 3.2, showing the mass-count disparity for

4 SPEC2000 benchmarks, one of which (*mcf*) is known for its poor cache utilization. The divergence between the distributions can be quantified by the joint ratio [20], which is a generalization of the proverbial 20/80 principle: This is the unique point in the graphs where the sum of the two CDFs is 1. In the case of the vortex data, for example, the joint ratio is approximately 13/87 (double-arrow at middle of plot). This means that 13% of the cache residencies, and more specifically those instances that are highly referenced, service a full 87% of the references, whereas the remaining 87% of the residencies service only 13% of the references. Thus a typical *residency* is only referenced a rather small number of times (up to about 10), whereas a typical *reference* is directed at a long residency (one that is accessed from 100 to thousands of times).

More important for this work are the  $W_{1/2}$  and  $N_{1/2}$  metrics [20]. The  $W_{1/2}$  metric assesses the combined weight of the half of the residencies that receive few references. For vortex, these 50% of the residencies together get ~3% of the references (left down-pointing arrow). Thus these are instances of blocks that are inserted into the cache but hardly used, and should actually not be allowed to pollute the cache. Rather, the cache should ideally be used preferentially to store longer residencies, such as those that together account for 50% of the references. The number of long residencies needed to account for half the references is quantified by the  $N_{1/2}$ metric; for vortex it is less than 1% (right up-pointing arrow). Table 3.1 lists the measured  $W_{1/2}$ ,  $N_{1/2}$  and joint-ratio data for the 20 SPEC2000 benchmarks used, along with the maximal residency length of the blocks accounting for  $W_{1/2}$ , and the minimal residency length of the blocks accounting for  $N_{1/2}$  (marked by the @ value). For vortex, the table reveals that the 50% of the data cache residencies are accessed up to 3 times, and that 50% of vortex's references are serviced by less than 1% of the residencies, each accessed over 500 times. All-in-all, the table reveals that half of the data references are serviced by less than 1% of all residencies, in 15 of the 20 benchmarks inspected.

The disparity is less apparent in benchmarks that are well known for their poor cache utilization such as *mcf*, *art*, *swim* and *lucas*. For example almost 96% of *mcf*'s residencies consist of no more than 5 references, but still they account for over 70% of the references. This is man-

Cache Residency Length (log)

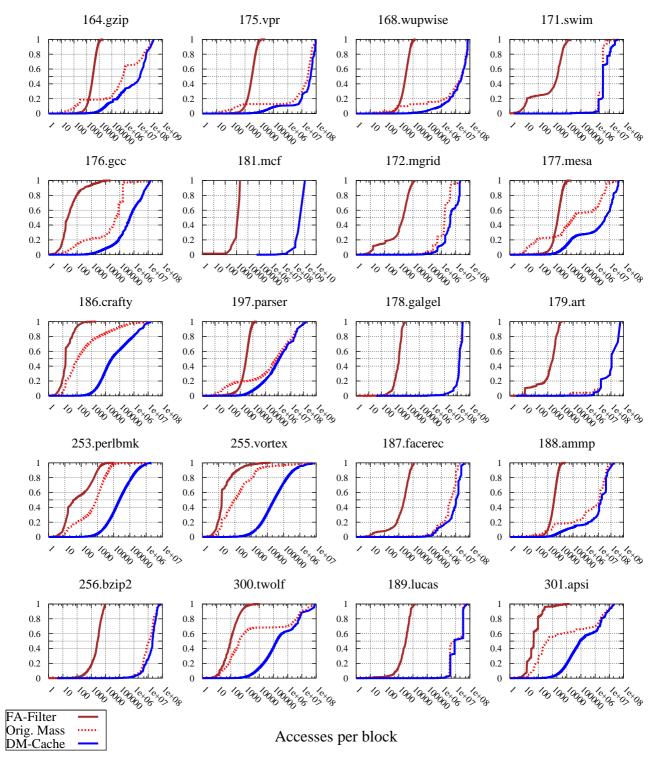

Figure 3.3: Mass-count disparity plots for **instruction** memory accesses in select SPEC2000 benchmarks. The arrows demonstrate the  $W_{1/2}$ , joint-ratio, and  $N_{1/2}$  metrics of mass-count disparity. Note that the mcf code is so dense that it has no residencies shorter than ~50000 references.

ifested in a joint ratio of 33/66, and relatively high  $W_{1/2}$  and  $N_{1/2}$  values — the weight of half the residencies  $(W_{1/2})$  is ~25% of the mass, and the ~17% longest residencies are required for half the mass  $(N_{1/2})$ . However, since the longest 3% of the residencies still compose 30% of the mass, *mcf* still exhibits some degree of disparity.

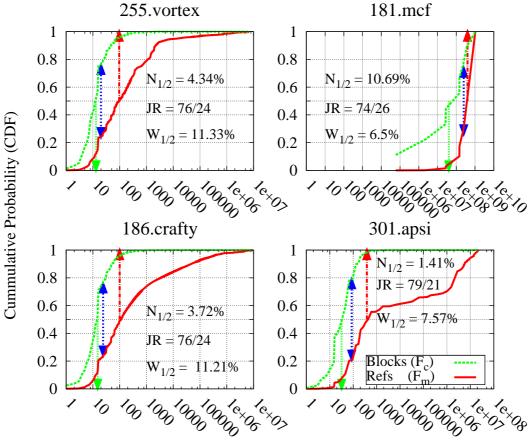

Evident in instruction streams as well, the mass-count disparity is not unique do data streams. Figure 3.3 shows the mass-count disparity plots for the instruction streams corresponding to Figure 3.2. We can see that the benchmarks still enjoy a  $W_{1/2}$  values of ~11% and less, indicating that the short residencies only service a fraction of all references. Further-

more, the  $N_{1/2}$  values are generally even lower, indicating the long residencies dominate the reference stream, and that the major bulk of the references are directed at a small fraction of the working set. The only exception to this is the  $N_{1/2}$  value for *mcf* which stands at ~10%. But this actually stems from *mcf*'s exceptional code density that results in a very small number of distinct instruction blocks accessed throughout the execution, which in turn yields a small number of very long residencies — the shortest of which is measured at ~10<sup>5</sup> references, as shown in Figure 3.3. It is the small number of residencies that skews *mcf*'s statistics. All in all, the benchmarks enjoy joint ratios of ~75/25 and up, suggesting that even these points — representing an equilibrium between short and long residencies — show a clear separation of the mass and the count distributions. The mass-count disparity exhibited by the instruction streams is in fact a manifestation of the well-known "rule-of-thumb" by which programs spend most of the time executing a small fraction of their code (described as the 90/10 rule by Hennessy and Patterson [27]).

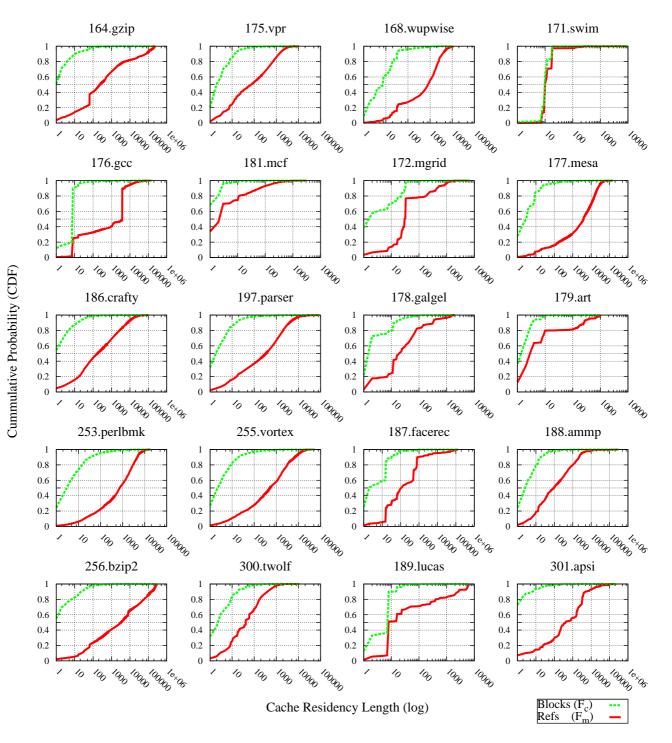

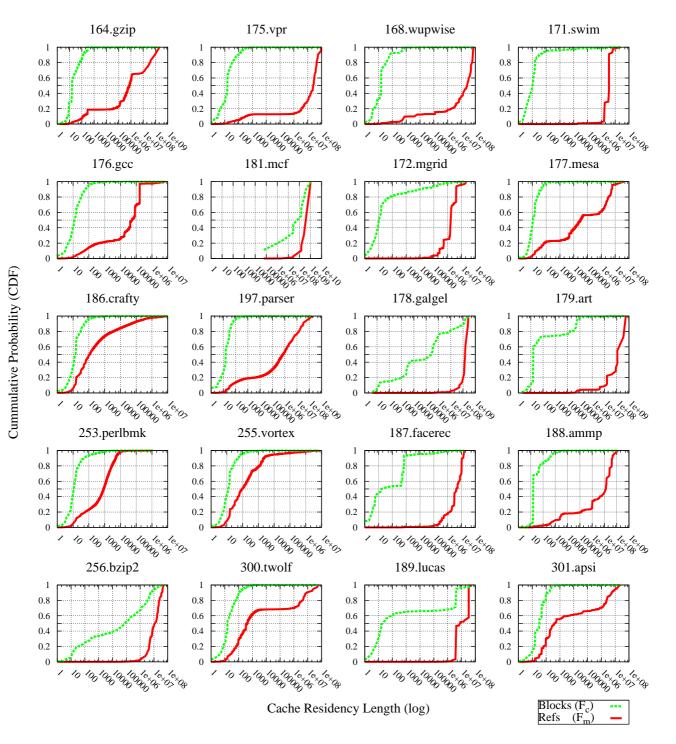

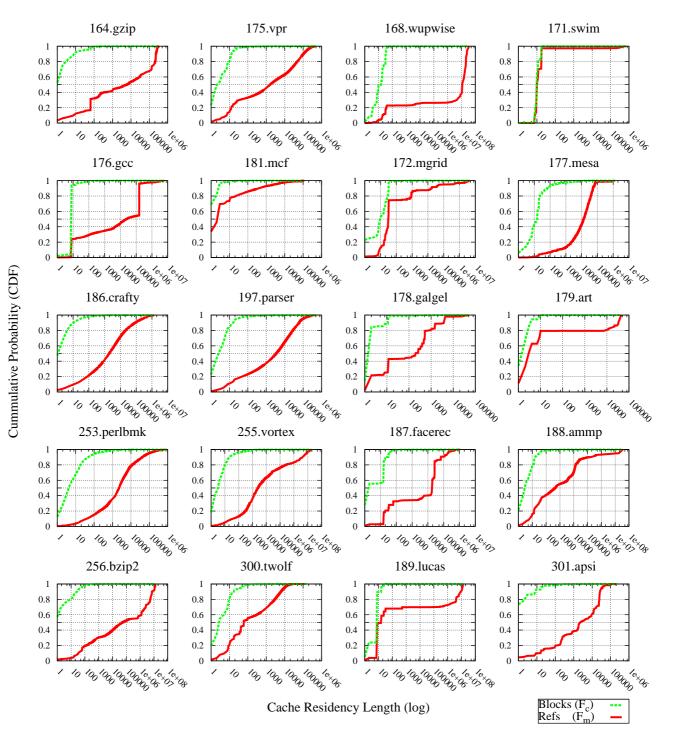

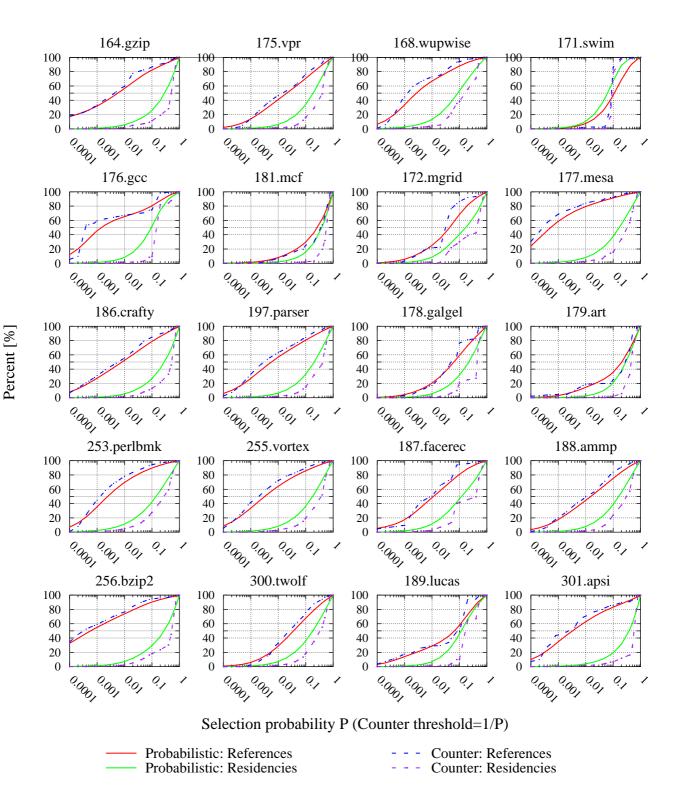

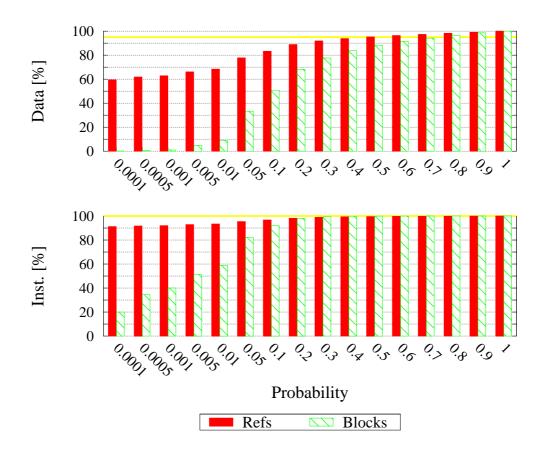

These results demonstrate the existence of a mass-count disparity stemming from the skewed distributions of memory accesses, for both data and instruction streams. While only select benchmarks are discussed here individually, this phenomenon is indeed consistent for all 20 SPEC2000 benchmarks analyzed. For completeness, all data streams' mass-count disparity plots are shown in Figure 3.4, and are accompanied by Table 3.1 listing the corresponding values of the different mass-count metrics. Figure 3.5 and Table 3.2 show the same for the instruction streams.

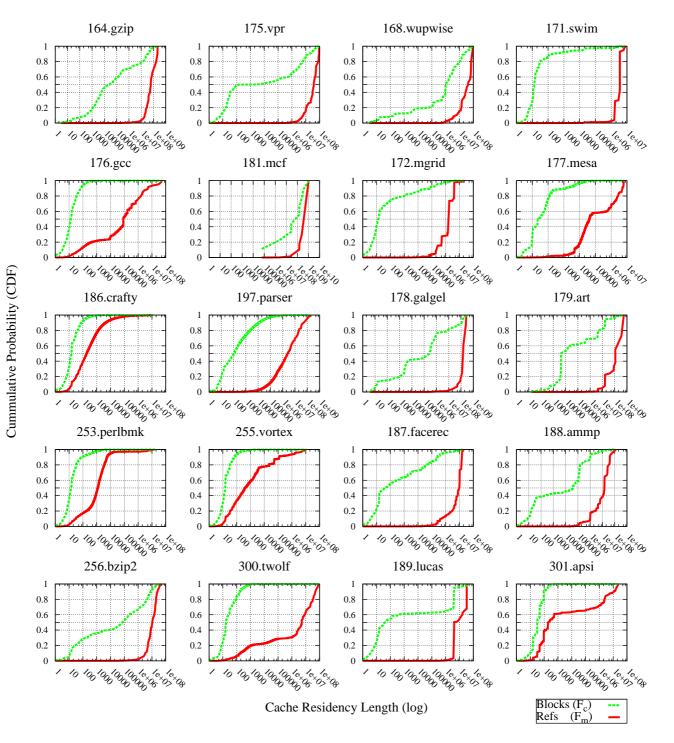

Although only figures for residencies in a direct-mapped cache are discussed here, the masscount disparity phenomenon is practically oblivious to cache associativity. Figure 3.6 and the corresponding metrics' values listed in Table 3.3 show the disparity observed for residencies in a 16K 4-way set-associative caches is very similar to that observed on similar size directmapped caches. This similarity repeats for the 4-way set-associative instruction stream results, as shown in Figure 3.7 and its corresponding metrics' values listed in Table 3.4.

Temporal locality of reference is one of the best-known phenomena in computer workloads [18, 32, 27], and is the foundation around which the computer's memory hierarchy is designed

[32, 27]. But mass-count disparity plots show that such locality is actually the result of two distinct properties: that references to the same address tend to come in batches, and that some addresses are much more popular than others [35]. The popular blocks are manifested by the long residencies that service the majority of references. Opposite, most short residencies are not degenerate and still have a noticeable length (albeit of a small number of references) indicating that even accesses to transient blocks are batched together as a burst of activity. Had these accesses not been bursty in nature, the block would have been evicted before it is reused and the residency length would have degenerated.

The existence of mass-count disparity demonstrates that the working set is not evenly used but is rather focused around a *core*. These more popular addresses can be grouped together to form the *core working set* — a subset of the Denning's classic working set definition [18] whose cache residencies naturally serve the majority of references. This has important consequences regarding random sampling. Specifically, if you pick a residency at random, there is a good chance that it is seldom referenced. That is why random replacement is a reasonable eviction policy, as has been observed many times [67, 70]. But if you pick *a reference* at random, there is a good chance that this reference refers to a block that is referenced very many times, thus belonging to the *core* of the working set.

Identifying the *core working set* can improve the efficiency of the caching mechanism, and the nature of this core allows it to be identified using random sampling.

Figure 3.4: **16KB Data cache, direct-mapped**: A general overview of the mass (references) and count (blocks) distributions for the **data** streams of all 20 SPEC2000 benchmarks reviewed. Together with the data from Table 3.1, this figure demonstrates that the mass-count disparity exists in practically all data streams.

| Benchmark   | $W_{1/2}$ | $W_{1/2}$ @ | $N_{1/2}$ | $N_{1/2}$ @ | JR       | JR@  |

|-------------|-----------|-------------|-----------|-------------|----------|------|

| 164.gzip    | 3.80      | 1           | 0.60      | 230         | 87 / 13  | 8    |

| 175.vpr     | 7.60      | 2           | 1.71      | 72          | 80 / 20  | 8    |

| 176.gcc     | 11.68     | 8           | 0.27      | 3826        | 79 / 21  | 8    |

| 181.mcf     | 24.77     | 1           | 16.79     | 3           | 67 / 33  | 1    |

| 186.crafty  | 4.39      | 1           | 0.69      | 169         | 86 / 14  | 8    |

| 197.parser  | 4.48      | 2           | 0.67      | 336         | 85 / 15  | 9    |

| 253.perlbmk | 2.29      | 3           | 0.93      | 731         | 88 / 12  | 25   |

| 255.vortex  | 3.25      | 3           | 0.65      | 517         | 87 / 13  | 15   |

| 256.bzip2   | 1.83      | 1           | 0.10      | 3247        | 90 / 10  | 24   |

| 300.twolf   | 7.34      | 3           | 4.39      | 42          | 78 / 22  | 9    |

| 168.wupwise | 3.59      | 8           | 1.07      | 804         | 84 / 16  | 32   |

| 171.swim    | 38.98     | 10          | 37.48     | 10          | 56 / 44  | 10   |

| 172.mgrid   | 5.34      | 2           | 10.41     | 30          | 77 / 23  | 17   |

| 177.mesa    | 2.01      | 3           | 0.20      | 3886        | 90 / 10  | 20   |

| 178.galgel  | 11.12     | 2           | 6.44      | 20          | 78 / 22  | 8    |

| 179.art     | 21.69     | 2           | 16.52     | 3           | 67 / 33  | 2    |

| 187.facerec | 3.41      | 2           | 2.32      | 104         | 80 / 20  | 16   |

| 188.ammp    | 5.88      | 3           | 1.85      | 96          | 81 / 19  | 12   |

| 189.lucas   | 18.24     | 8           | 11.44     | 8           | 67 / 33  | 8    |

| 301.apsi    | 4.81      | 1           | 0.26      | 396         | 89 / 11  | 6    |

| Average     | 9.33      | 3.3         | 5.74      | 726         | 80 / 20  | 12.3 |

| Median      | 5.34      | 2           | 1.71      | 169         | 81 / 20* | 0    |

Table 3.1: **16KB Data cache, direct-mapped**: The  $N_{1/2}$  and  $W_{1/2}$  metrics values for L1 **data** streams of the 20 SPEC2000 benchmarks used.

\* Median Joint-Ratio values are independent and thus may not sum up to 100%.

Figure 3.5: **16KB Instruction cache, direct-mapped**: A general overview of the mass (references) and count (blocks) distributions for the **instruction** streams of all 20 SPEC2000 benchmarks reviewed. Together with the data from Table 3.2, this figure demonstrates that the mass-count disparity exists in practically all data streams.

| Benchmark   | $W_{1/2}$ | $W_{1/2}$ @ | $N_{1/2}$ | $N_{1/2}$ @ | JR       | JR@     |

|-------------|-----------|-------------|-----------|-------------|----------|---------|

| 164.gzip    | 2.20      | 16          | 0.00      | 7.2 e+5     | 90 / 10  | 123     |

| 175.vpr     | 1.43      | 16          | 0.00      | 2.5 e+7     | 93 / 7   | 144     |

| 176.gcc     | 2.74      | 13          | 0.05      | 5.4 e+4     | 89 / 11  | 59      |

| 181.mcf     | 6.50      | 1.46 e+8    | 10.69     | 1.0 e+9     | 74 / 26  | 2.5 e+8 |

| 186.crafty  | 11.21     | 15          | 3.72      | 112         | 76 / 24  | 24      |

| 197.parser  | 3.16      | 16          | 0.00      | 7.2 e+5     | 89 / 11  | 48      |

| 253.perlbmk | 5.91      | 12          | 1.48      | 858         | 84 / 16  | 30      |

| 255.vortex  | 11.33     | 13          | 4.34      | 96          | 76 / 24  | 20      |

| 256.bzip2   | 0.19      | 7.5 e+4     | 5.22      | 1.2 e+7     | 82 / 18  | 4.3 e+6 |

| 300.twolf   | 6.32      | 16          | 1.91      | 416         | 81 / 19  | 64      |

| 168.wupwise | 0.65      | 16          | 0.00      | 2.6 e+7     | 95 / 5   | 512     |

| 171.swim    | 0.01      | 11          | 0.46      | 3.5 e+6     | 99 / 1   | 6.7 e+5 |

| 172.mgrid   | 0.00      | 11          | 1.03      | 1.8 e+6     | 95 / 5   | 2.0 e+5 |

| 177.mesa    | 4.65      | 11          | 0.02      | 3.0 e+4     | 87 / 13  | 32      |

| 178.galgel  | 0.06      | 2.7 e+5     | 5.33      | 1.6 e+8     | 88 / 12  | 8.6 e+6 |

| 179.art     | 0.00      | 16          | 0.04      | 1.1 e+8     | 97 / 3   | 6.4 e+4 |

| 187.facerec | 0.01      | 16          | 0.28      | 4.6 e+6     | 97 / 3   | 1.8 e+5 |

| 188.ammp    | 1.02      | 16          | 0.00      | 1.3 e+7     | 94 / 6   | 448     |

| 189.lucas   | 0.00      | 20          | 3.94      | 8.4 e+6     | 80 / 20  | 4.2 e+6 |

| 301.apsi    | 7.57      | 32          | 1.41      | 384         | 79 / 21  | 86      |

| Average     | 3.25      | 7.3 e+6     | 2.00      | 7.0 e+7     | 87 / 13  | 1.7 e+7 |

| Median      | 2.20      | 16          | 1.03      | 3.5 e+6     | 89 / 12* | 448     |

Table 3.2: **16KB Instruction cache, direct-mapped**: The  $N_{1/2}$  and  $W_{1/2}$  metrics values for L1 instruction streams of the 20 SPEC2000 benchmarks used.

$^{\ast}$  Median Joint-Ratio values are independent and thus may not sum up to 100%.

Figure 3.6: **16KB Data cache, 4-way set-associative**: A general overview of the mass (references) and count (blocks) distributions for the **data** streams of all 20 SPEC2000 benchmarks reviewed. Together with the data from Table 3.3, this figure demonstrates that the mass-count disparity exists in practically all data streams.

| Benchmark   | $W_{1/2}$ | $W_{1/2}$ @ | $N_{1/2}$ | $N_{1/2}$ @ | JR      | JR@ |

|-------------|-----------|-------------|-----------|-------------|---------|-----|

| 164.gzip    | 3.22      | 1           | 0.02      | 6005        | 89 / 11 | 8   |

| 175.vpr     | 4.41      | 3           | 0.09      | 1606        | 84 / 16 | 11  |

| 176.gcc     | 12.40     | 8           | 0.01      | 24085       | 80 / 20 | 8   |

| 181.mcf     | 24.47     | 1           | 16.00     | 3           | 67 / 33 | 1   |

| 186.crafty  | 2.49      | 2           | 0.14      | 1932        | 90 / 10 | 11  |

| 197.parser  | 3.21      | 3           | 0.10      | 3441        | 88 / 12 | 14  |

| 253.perlbmk | 1.83      | 5           | 0.52      | 2277        | 90 / 10 | 45  |

| 255.vortex  | 1.75      | 4           | 0.20      | 2528        | 91 / 9  | 26  |

| 256.bzip2   | 1.35      | 1           | 0.00      | 52757       | 91 / 9  | 32  |

| 300.twolf   | 6.79      | 3           | 1.79      | 60          | 79 / 21 | 10  |

| 168.wupwise | 4.45      | 16          | 0.00      | 11565917    | 85 / 15 | 32  |

| 171.swim    | 39.50     | 10          | 37.81     | 10          | 56/44   | 10  |

| 172.mgrid   | 11.51     | 10          | 14.55     | 32          | 71 / 29 | 21  |

| 177.mesa    | 1.51      | 16          | 0.36      | 13377       | 93 / 7  | 124 |

| 178.galgel  | 11.99     | 2           | 0.61      | 198         | 80 / 20 | 2   |

| 179.art     | 21.75     | 2           | 15.74     | 3           | 67 / 33 | 3   |

| 187.facerec | 2.30      | 2           | 0.05      | 17920       | 83 / 17 | 16  |

| 188.ammp    | 5.17      | 3           | 0.25      | 444         | 82 / 18 | 14  |

| 189.lucas   | 21.92     | 8           | 10.24     | 16          | 67 / 33 | 8   |

| 301.apsi    | 3.04      | 1           | 0.07      | 2232        | 91 / 9  | 9   |

| Average     | 9.25      | 5           | 4.93      | 584742      | 81 / 19 | 20  |

| Median      | 4.45      | 3           | 0.25      | 2232        | 84 / 17 | 11  |

Table 3.3: **16KB Data cache, 4-way set-associative**: The  $N_{1/2}$  and  $W_{1/2}$  metrics values for L1 **data** streams of the 20 SPEC2000 benchmarks used.

$^{\ast}$  Median Joint-Ratio values are independent and thus may not sum up to 100%.

Figure 3.7: **Instruction cache, 4-way set-associative**: A general overview of the mass (references) and count (blocks) distributions for the **instruction** streams of all 20 SPEC2000 benchmarks reviewed. Together with the data from Table 3.4, this figure demonstrates that the mass-count disparity exists in practically all data streams.

| Benchmark   | $W_{1/2}$ | $W_{1/2}$ @ | $N_{1/2}$ | $N_{1/2}$ | JR      | JR@     |

|-------------|-----------|-------------|-----------|-----------|---------|---------|

| 164.gzip    | 0.02      | 2.5 e+4     | 4.58      | 6.0 e+7   | 85 / 15 | 2.3 e+7 |

| 175.vpr     | 0.00      | 144         | 4.73      | 3.8 e+7   | 85 / 15 | 9.9 e+6 |

| 176.gcc     | 2.63      | 14          | 0.02      | 8.4 e+4   | 89 / 11 | 65      |

| 181.mcf     | 6.50      | 146 e+8     | 10.69     | 1.0 e+9   | 74 / 26 | 2.5 e+8 |

| 186.crafty  | 8.81      | 16          | 3.83      | 190       | 78 / 22 | 36      |

| 197.parser  | 0.05      | 108         | 0.14      | 2.6 e+6   | 94 / 6  | 3.1 e+4 |

| 253.perlbmk | 4.32      | 14          | 1.81      | 1.2 e+3   | 86 / 14 | 52      |

| 255.vortex  | 8.08      | 16          | 1.29      | 405       | 80 / 20 | 32      |

| 256.bzip2   | 0.15      | 6.9 e+4     | 7.04      | 1.0 e+7   | 82 / 18 | 4.9 e+6 |

| 300.twolf   | 1.68      | 18          | 0.00      | 5.2 e+6   | 91 / 9  | 176     |

| 168.wupwise | 2.45      | 1.0 e+6     | 5.66      | 4.2 e+7   | 82 / 18 | 1.3 e+7 |

| 171.swim    | 0.01      | 14          | 0.89      | 3.5 e+6   | 98 / 2  | 1.1 e+6 |

| 172.mgrid   | 0.00      | 14          | 1.39      | 1.8 e+6   | 93 / 7  | 2.0 e+5 |

| 177.mesa    | 0.30      | 27          | 0.35      | 4.2 e+4   | 93 / 7  | 4.5 e+3 |

| 178.galgel  | 0.06      | 2.7 e+5     | 5.33      | 1.6 e+8   | 88 / 12 | 8.6 e+7 |

| 179.art     | 0.01      | 4.4 e+3     | 1.75      | 1.1 e+8   | 87 / 13 | 1.6 e+7 |

| 187.facerec | 0.00      | 45          | 1.24      | 9.8 e+6   | 92 / 8  | 3.9 e+5 |

| 188.ammp    | 0.19      | 3.8 e+4     | 1.50      | 1.5 e+7   | 89 / 11 | 1.0 e+6 |

| 189.lucas   | 0.00      | 42          | 5.14      | 4.2 e+6   | 78 / 22 | 4.2 e+6 |

| 301.apsi    | 10.17     | 32          | 2.93      | 208       | 76 / 24 | 72      |

| Average     | 2.27      | 7.4 e+6     | 3.02      | 7.5 e+7   | 86 / 14 | 2.1 e+7 |

| Median      | 0.19      | 45          | 1.81      | 5.2 e+6   | 87 / 14 | 1.0 e+6 |

Table 3.4: **16KB Instruction cache, 4-way set-associative**: The  $N_{1/2}$  and  $W_{1/2}$  metrics values for L1 instruction streams of the 20 SPEC2000 benchmarks used.

$^{\ast}$  Median Joint-Ratio values are independent and thus may not sum up to 100%.

## Chapter 4

# **Core Working Sets: Capturing the Dual Nature of Memory Workloads**

Locality is usually regarded as a combination of two distinct properties — locality in time and locality in space. But it is also a manifestation of the skewed distribution of the *popularity* of different memory blocks, where some blocks are accessed more frequently than others. In fact, as shown below, it may be possible to partition the working set into two sub-sets: those data items that are very popular and accessed at a very high rate, and those that are only accessed intermittently. This distinction is antithetical to Denning's definition which puts all items in a working set on an equal footing, and lies at the heart of the definition of the *core* of the working set.

The notion of a core leads to the realization that not all elements of the working set are equally important. The elements in the working set are not accessed in a homogeneous manner. Thus treating all the elements of the working set equally may lead to sub-optimal performance. Rather, it may be beneficial to try to identify the more important core elements, and give them preferential treatment.

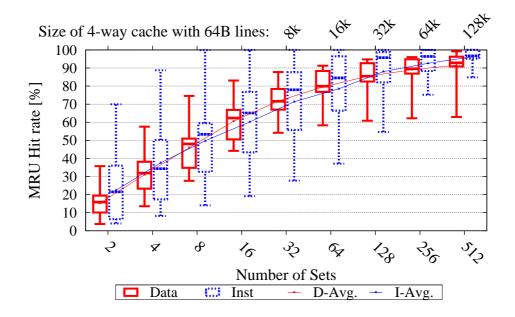

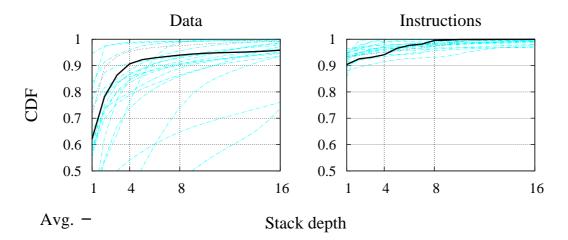

A striking manifestation of a "hot" core within the working set can be seen when exploring the stack depths accessed in a set-associative cache's sets, and more specifically as the fraction of references serviced by the cache sets' most recently used (MRU) blocks. Figure 4.1 presents

Figure 4.1: Fraction of accesses serviced by the most recently used (MRU) blocks in a cache's sets for various cache configurations. The top axis show the size of 4-way set-associative cache (with 64B cache lines) corresponding to each number of sets. Results are shown as an average over all SPEC2000 benchmarks surveyed.

the fraction of memory references serviced by the MRU blocks in the cache sets for various cache configurations. This is achieved by simply varying the numbers of cache sets examined (the metric is oblivious to the cache's exact associativity as it only examines MRU accesses). The X axis in the Figure indicates a number of sets in the cache, and the box-plots represent the MRU access statistics for all SPEC2000 benchmarks given a specific number of cache sets — where each box-plot shows the 25-75 percentiles, minimum and maximum values, median and the average (marked with a circle) over all benchmarks. The Figure shows that as the number of cache sets increases, more references are serviced by the MRU blocks in the referenced set: for caches with at least 128 sets an average of ~85% of all memory references (data and instructions) are serviced by the MRU blocks, with even the 25th percentile crossing the 80% threshold. When the number of sets doubles to 256 the MRU hits reach ~90% of all references. The reason for the dependence on the number of sets in the cache is the small set of blocks servicing the majority of references, and how it is distributed among the cache sets: as the number of cache sets increases the number of mapping conflicts between the core blocks

decreases, thus enabling this small set of blocks — the core of the working set — to be evenly distributed between the different sets. When the number of set suffices, each set contains on average at most a single block from the working set's core. As the core is accessed repeatedly, its blocks maintain their MRU positions.

The Figure also shows the size of a 4-way set-associative cache corresponding to the number of cache sets displayed. Interestingly, modern processors such as the Intel Core product series [29] and AMD Phenom series [1] use 32K and 64K L1 caches, respectively, thereby serving an average of ~90% of all memory references from the sets' MRU positions. In fact, since the AMD Phenom uses a 64K 2-way set-associative cache, it has double the number of sets than a similar size 4-way set-associative cache — thus enjoying an even higher ~95% MRU hits.

This chapter introduces a formal framework that extends and refines Denning's definition of a working set, enabling designers to explicitly express their perception of which blocks in the working set are considered important. This framework uses logical predicates to distinguish between the important subset — the core — and the remaining blocks. An example of a predicate that can be used to identify the core is "the block is accessed at least 16 times when brought into the cache". The extraction of an explicit predicate enables qualitative comparison between different caching mechanisms and implementations. In particular, it decouples the *notion* of the working set's core from the actual *caching mechanism* used to implement it.

While the core working set framework is aimed for use with any caching mechanism, this exploration is focused on the synergy between the skewed distribution of memory references and dual cache structures. Defining the core based on the intensity of memory references naturally leads to a dual design, where one part of the cache is used for the core data, while the more transient data is served by another part. In effect this filters non-core data and prevents them from polluting the cache structure used for core data.

### 4.1 Definition of Core Working Sets

Denning's definition of working sets [17] is based on the principle of locality, which he defined to include three components [19]: a nonuniform popularity of different addresses, a slow change in the reference frequency to any given page, and a correlation between the immediate past the near future. Our data strongly supports the first component, that of non-uniform access. But it casts a doubt on the other two, by demonstrating the continued access to the same high-use memory objects, while much of the low-use data is only accessed for very short and intermittent time windows. In addition, transitions between phases of the computation may be expected to be sharp rather than gradual, and moreover, they will probably be correlated for multiple memory objects. This motivates a new definition that focuses on the persistent high-usage data in each phase, namely the core working set.

The definition of a working set by Denning is the set of *all* distinct blocks that were accessed within a window of T instructions [17]. This set will be denoted as  $D_T(t)$ , to mean "the Denning working set at time t using a window size of T". Our findings imply that this definition is deficient in the sense that it does not distinguish between the heavily used items and the lightly used ones.

As an alternative, we define the *core working set* to be those blocks that appear in the working set and are reused a significant number of times. This will be denoted  $C_{T,P}(t)$ , where the extra parameter P reflects a predictor used to identify core members; the predictor will be expressed as a predicate that evaluates to "true" for core members, and "false" for other blocks. This is a generalization of the Denning working set, which can simply be expressed as the core working set with a predicate that is always true:

$$D_T(t) \equiv C_{T,\text{true}}(t)$$

The predicate P is meant to capture reuse of memory. In the context of virtual memory, temporal locality has been used to justify page replacement algorithms such as LRU or the clock algorithm. In particular, Belady emphasized the importance of use bits to identify recently

used data that should be retained [6]. Our reuse predictors can be seen as an extension of this practice. The generality of core working sets can also be demonstrated by its applicability to block prefetchers: at any time t, a prefetcher would estimate the core at a future time t + n. Therefore, the prefetcher's core can be described as  $C_{T,P}(t + n)$ , where P represents the predicate best describing the prefetcher designer's perception of the important subset of blocks.

The simplest reuse predictor is based on counting the number of references to a given block (or the number of references during a residency). Let B represent a block of k words. Let  $w_i$ , i = 1, ..., k be the words in block B. Let r(w) be the number of references to word w within the window of interest. Using this, we can define the predicate nB that evaluates to true if block B was referenced n times or more:

$$n\mathbf{B} \equiv \sum_{i=1}^{k} r(w_i) \ge n$$

For example, the predicate 3B identifies those blocks that were referenced a total of 3 times or more.

The nB predicates are meant to identify a combination of spatial and/or temporal locality, without requiring either type explicitly. Alternatively, we can write a temporal-locality predicate that requires that some specific word w in block B was referenced n times or more:

$$n\mathbf{W} \equiv \exists w \in B \text{ s.t. } r(w) \ge n$$

We can also write a predicate that requires a certain number of distinct words to be referenced, to express spatial locality.

An example of a more complicated predicate is the  $n \times ST$  predicate, which is meant to identify a non-uniform strided reference pattern with reuse. This predicate is designed to filter out memory scans that use strided access, even if they include up to n accesses to the same memory location within the scan. This is done by tabulating the last few accesses, as illustrated by the following pseudocode (where addr is the address accessed last):

```

if (prev_addr == addr) {repeat++;}

else {prev_stride = stride; stride = addr - prev_addr; repeat = 0;}

prev_addr = addr;

```

using this data, a block is considered in the core if it was accessed with inconsistent strides, or if a single word was referenced more than n times in a row. Formally, this is written as

$$n \times ST \equiv (repeat > n) \lor (stride \neq prev\_stride)$$

These examples only demonstrate the richness of the predicates' design space. But given the rich set of possible predicates, the question is how to select one that captures the notion of a core working set. Based on the discussion about the bursty nature of access patterns (Section 3.2), it seems advisable to require a significant number of references. In particular, we have found 16B to be a promising predicate.

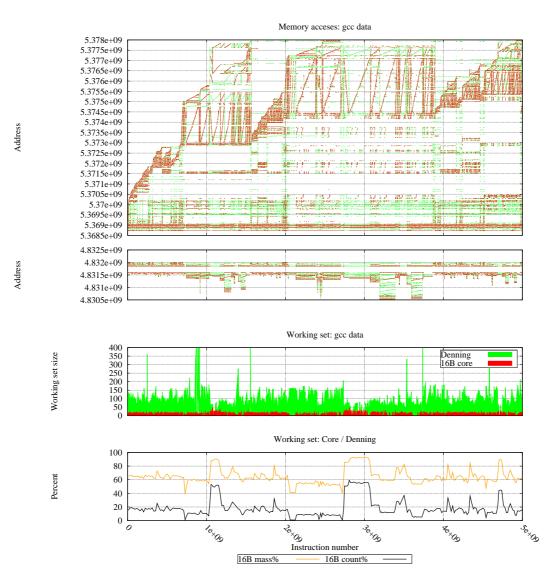

The application of a core working set is illustrated in Figure 4.2. Using the SPEC gcc benchmark as an example, the top graph simply shows the access pattern to the data. Below it we show the Denning working set  $D_{1000}(t)$  (i.e. for a window of 1000 instructions) and the core working set  $C_{1000,16B}(t)$ . As we can easily see, the core working set is indeed much smaller, typically being just 10–20% of the Denning working set. Importantly, it eliminates all of the sharp peaks that appear in the Denning working set. Nevertheless, as shown in the bottom graph, it routinely captures about 60% of the memory references.

### 4.2 Core Working Sets and Dual Cache Structures

We have established that memory blocks can be roughly divided into two groups: the *core* working set, which includes a relatively small number of blocks that are accessed a lot, and the rest, which are accessed only a few times in a bursty manner. The question then is how this can be put to use to improve caching.

The principle behind optimal cache replacement is very simple: when space is needed,

Figure 4.2: Examples of data memory access patterns and the resulting Denning and core working sets. The bottom plot shows that while the 16B core working set is composed of only  $\sim$ 20% of the blocks in Denning's working set, it still services some  $\sim$ 60% of its references.

replace the item that will not be used for the most time in the future (or never) [6]. In particular, it should be noticed that it is certainly possible that the optimal algorithm will decide to replace the *last* item that was brought into the cache, if all other items will be accessed before this item is accessed again. This would indicate that the item was only inserted into the cache as part of the mechanism of performing the access; it was not inserted into the cache in order to retain it for future reuse. Such blocks were appropriately described as dead-on-arrival (DOA) by Qureshi et al. [54].

By analyzing the reference streams of SPEC2000 benchmarks it is possible to see that this sort of behavior does indeed occur in practice. For example, we found that if the references of the *gcc* benchmark were to be handled by a 16 KB fully-associative cache, 30% of insertions would belong to this class; in other benchmarks, we saw results ranging from 13% to a whopping 86%. Returning to *gcc*, if the cache is 4-way set associative the placement of new items is much more restricted, and a full 60% of insertions would be immediately removed by the optimal algorithm. These results imply that the conventional wisdom favoring the LRU replacement algorithm is of questionable merit.

It is especially easy to visualize why LRU may fail by considering transient streaming data. When faced with such data, the optimal algorithm would dedicate a single cache line for all of it, and let the data stream flow through this cache line. All other cache lines would not be disturbed. *Effectively, the optimal algorithm thus partitions the cache into the main cache (for core non-streaming data) and a cache bypass for the streaming component (non-core).* The LRU algorithm, by contradistinction, would do the opposite and lose all the cache contents.

The aforementioned benefits of using a cache bypass can be demonstrated formally using a simple, specific example cache configuration. Assume a cache with  $n^2 + n$  cache lines, organized into n sets whose size is either n or n+1 cache lines each. In either case, the address space is partitioned into n equal-size disjoint partitions (assuming n is a power of 2) using the memory address bits. The two organizations are used as follows.

Set associative: there are n sets of n + 1 cache lines each, and each serves a distinct partition of the address space. This is the commonly used approach.

**Bypass:** there are n sets of n cache lines each, and each serves a distinct partition of the address space, as in the conventional approach. The remaining n cache lines are grouped as a disjoint set (which we will call the "extra" set), and can accept any address and serves as a bypass. <sup>1</sup>

These two designs expose a tradeoff: in the set associative design, each set is larger by one, reducing the danger of conflict misses. In the bypass design, the extra set is not tied to any specific address, increasing flexibility.

Considering these two options, it is relatively easy to see that the bypass design has the advantage. Formally this is shown by two claims.

#### **Claim 1** *The bypass design can simulate the set associative design.*

**Proof:** While each cache line in the extra set can hold any address from the address space, we are not required to use this functionality. Instead, we can limit each cache line to one of the partitions in the address space. Thus the effective space available for caching each partition becomes n + 1, just like in the set associative design.

The conclusion from this claim is that the bypass design need never suffer more cache misses than the set associative design. At the same time, we have the following claim that establishes that it actually has an advantage.

**Claim 2** There exist access patterns that suffer arbitrarily more cache misses when served by the set associative design than when served by the bypass design.

**Proof:** An access pattern that provides such an example is the following: repeatedly access 2n addresses from any single address space partition in a cyclic manner m times. When using the set associative design, only a single set with n cache lines will be used. At best, an arbitrary subset of n - 1 addresses will be cached, and the other n + 1 will share the remaining cell, leading to a total of O(nm) misses. When using the bypass design, on the other hand, all 2n

<sup>&</sup>lt;sup>1</sup>For simplicity, the claims assume the bypass buffer contains the same number of ways as sets in the main cache — but obviously these numbers need not be the same.

addresses will be cached by using the original set and the extra set. Therefore only the initial 2n compulsory misses will occur. In this sense, a bypass mechanism can potentially relieve pressure on specific cache sets resulting from bursty conflict misses. By extending the length of this pattern (i.e. by increasing m) any arbitrary ratio can be achieved.

An example of a dual-cache design that extends a simple set-associative cache is the *Victim Cache* proposed by Jouppi [37]. The victim cache includes a small fully-associative buffer into which all memory blocks evicted from the direct-mapped main cache (the "victims") are inserted. Jouppi showed that many of the blocks evicted from the main cache will be requested again within a short period of time, and should therefore be kept in an auxiliary cache and be given a chance for re-insertion. In that sense, the auxiliary buffer — called the *victim buffer* — serves as an extension to the main cache. The myriad of dual-cache structures proposed in the literature are discussed in Chapter 7.

The definition of *core working sets* thus extends the classic working set definition by Denning to capture the dual nature of memory workloads, and directly corresponds with the dualcache paradigm. While the paradigm itself is not new, the formalization of core working sets is novel. Core working sets thus enable cache designers to formally describe, compare and contrast dual-cache designs in a natural way — thereby adding a useful tool to the cache designer's toolbox.

# Chapter 5

# Cache Filtering Through Probabilistic Prediction of Temporal Locality

The existence of lengthy cache residencies is a direct result of temporal locality — as discussed in Section 3.1 — since frequent accesses to a block prevent it from being replaced in a standard LRU based set-associative cache. But even long residencies are sometimes terminated in favor of shorter residencies, when a more popular block is evicted in favor of a less popular one. This is commonly caused by changes in a program's memory workload that increase the number of cache misses (and therefore cache insertions) momentarily, and mainly affects caches with a relatively low degree of associativity that cannot effectively sustain a sudden burst of cache insertions. Although frequently accessed blocks will be quickly re-inserted into the cache, the first access after the eviction will incur a high latency cache miss. This is in fact the rationale behind the *least-frequently-used* (LFU) replacement policy.

Alternatively, these inefficient replacements can be avoided by employing a *cache insertion policy* that will prevent transient blocks from being inserted to cache in the first place — because such blocks effectively just pollute the cache. The length of a cache residency can thus serve as a metric for cache efficiency, with longer residencies indicating better efficiency, as the initial block insertion overhead (latency and power) is amortized over many cache hits. A simple filter can therefore be based on a residency length predictor that will be used to predict

whether inserting a block into the cache would be beneficial. If the insertion is not beneficial, references to the block can be served from an auxiliary buffer, or bypass the cache altogether (these two alternatives are effectively equivalent since the latter can be seen as using an auxiliary buffer containing a single block).

However, the definition of a "beneficial insertion" is not trivial, and is tightly coupled with the specifics of the cache design. Therefore, the discussion on residency length prediction (or rather whether a residency should be characterized as a long one) is separated from the proposed cache design (discussed in Chapter 6).

# 5.1 On the Non-Feasibility of an Optimal Insertion Policy for Dual-Cache Structures

Caches are commonly evaluated using their achievable miss-rate (or hit-rate), which, for simple associative cache structures, can be minimized using Belady's optimal replacement policy [6]. Using an insertion policy however, implies a dual-cache structure since the block selection can be effectively viewed as making a decision whether to insert the block into the cache itself, or rather into an auxiliary buffer. Although in general the auxiliary buffer can contain only one block — thus effectively implementing a cache bypass — it is assumed here that the auxiliary buffer contains more than one block.

Dual-cache structures are not addressed by Belady's optimal algorithm which only accounts for a replacement policy, and not a cache/buffer arbitration policy. Moreover, Brehob et al. showed that optimal cache replacement is NP-Hard for dual-caches in which one component is fully-associative and the other is either set-associative or direct-mapped [7]. This result can be extended to show that even if both caches are set-associative but with different numbers of sets, the problem is still NP-Hard — thereby removing the requirement that one of the components is fully-associative:

Claim 3 An optimal replacement algorithm for a dual-cache, in which both components are

set-associative with different number of sets, is NP-Hard if<sup>4</sup>:

- the numbers of sets in both components are powers of 2.

- the address bits used to map addresses to sets in the component containing the smaller number of sets, is a subset of the mapping bits in the other component.

**Proof:** Consider a dual-cache containing two set-associative components, where component 1 is of size  $B_1$  blocks and associativity of  $A_1$  (such that it is not fully-associative, i.e.  $A_1 < B_1$ ), and where component 2 is of size  $B_2$  and associativity  $A_2$  (such that  $A_2 < B_2$ ). Component 1 therefore contains  $S_1 = \frac{B_1}{A_1}$  disjoint sets, and component 2 contains  $S_2 = \frac{B_2}{A_2}$  sets. Based on the precondition,  $S_1 \neq S_2$ .

Now, let us assume (without loss of generality) that component 2 contains more sets than component 1, i.e.  $S_2 > S_1$ . We can therefore divide the entire reference stream into  $S_1$  disjoint reference sub-streams  $R_1 \cdots R_{S_1}$ , where each sub-stream  $R_i$  is mapped to, and uniquely serviced by, a single set in component 1. In addition, because the address bits used in mapping addresses to cache sets in component 1 are said to be subset of those used in component 2,  $R_i$  is also mapped to, and uniquely serviced by, exactly  $\frac{S_2}{S_1}$  sets in component 2. Furthermore, based on the precondition that  $S_1$  and  $S_2$  are distinct powers of 2, it is guaranteed that  $\frac{S_2}{S_1}$  is a natural number.

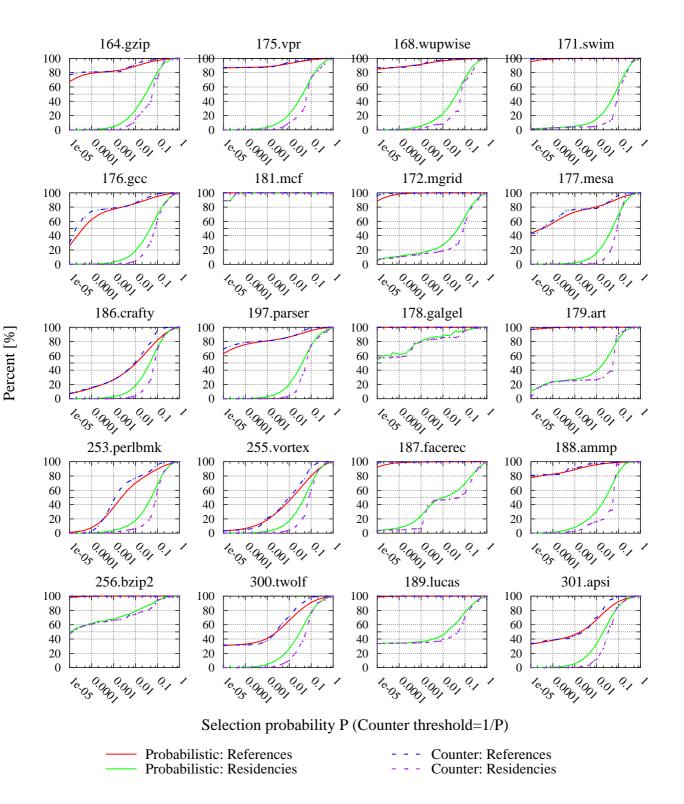

The entire dual-cache can thus be regarded as  $S_1$  disjoint dual-caches  $C_1 \cdots C_{S_1}$ , each containing a single set from component 1 and  $\frac{S_2}{S_1}$  sets from component 2 — with each  $C_i$  servicing only part of the entire reference stream, namely the  $R_i$  sub-stream. But each  $C_i$  is effectively a dual-cache composed of a fully-associative structure (the single set from component 1), and a set-associative cache of degree  $A_2$  and size  $A_2 \times \frac{S_2}{S_1}$  — a design for which an optimal replacement policy is NP-Hard according to Brehob et al.